射频问答群问答汇总·第90期【2025.07.23】

调完的模组放几天后性能变差,烘干又恢复是怎么回事?投票占比:46%

本文中回答均由各位射频从业者们自发讨论回复,回答之中不免有错误疏漏,也欢迎大家批评指正。

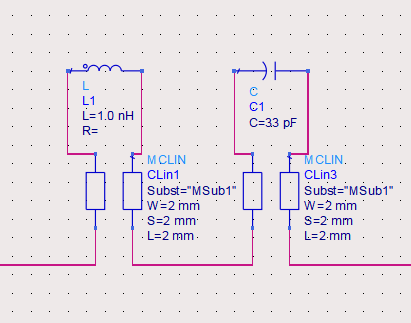

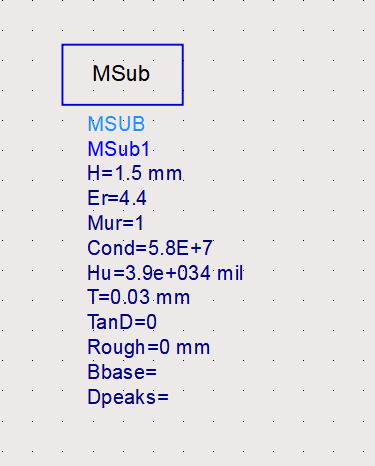

ADS 中含 substrate 信息的 symbol,仿真时为何仍需添加 substrate 组件?

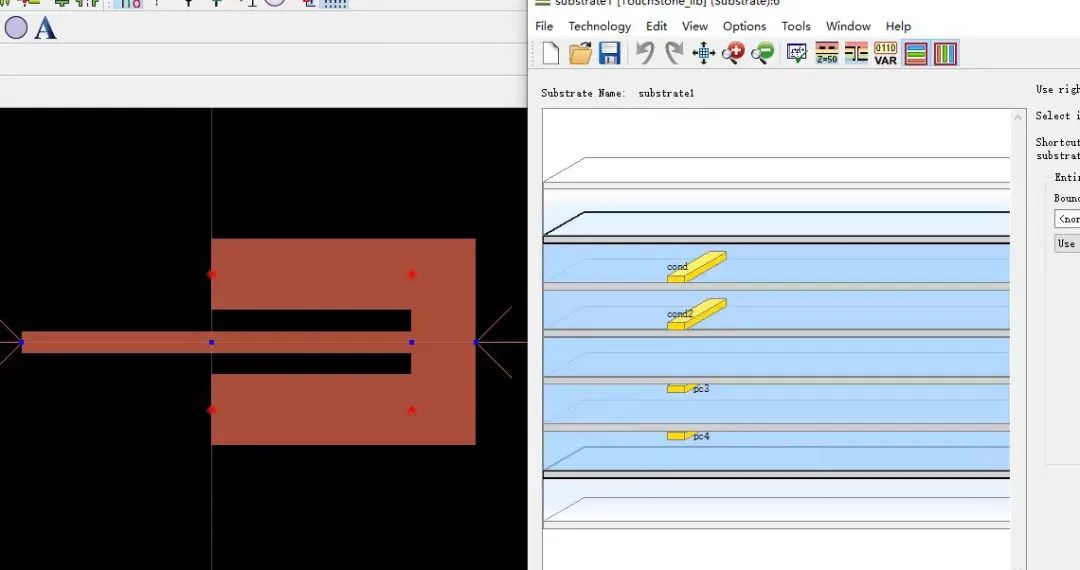

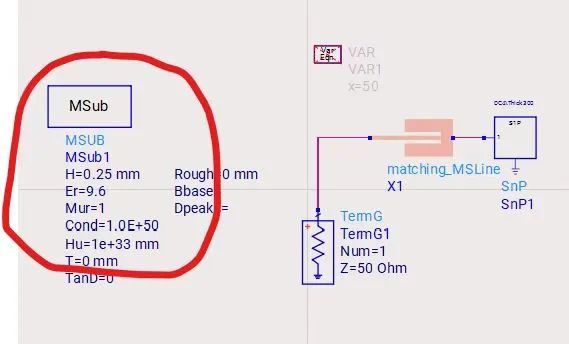

Q:各位好,我想请教一下我用ADS建立了一个微带线原件的symbol,这个symbol中已经包含了substrate的详细信息,后续我在原理图中使用这个symbol,还会提示我再添加一个substrate的组件,那么我仿真的时候使用的substrate的信息是哪几个呢?

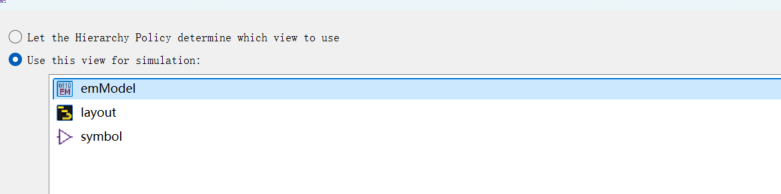

A:你忘记设置了,所以才需要添加组件,点在symbla上,然后点这里:

选择em model设置下,就不需要组件了。

这样子使用的就是EM设置里面的的板材和em的仿真结果了。

Q:哦哦!是这样的,可以了,谢谢!郁闷好半天。

搭建 LNA 用 ADS 还是 Systemvue 更合适?

Q:请问各位前辈,如果想选择芯片搭建一个LNA的话,用什么软件仿真比较好啊,ADS或者Systemvue可以吗?芯片的封装模型一般上哪里可以下载呀?今天找了几款比较符合要求的芯片但是都没找到封装模型。

A:个人认为ADS仿真如何设计LNA,比如稳定性,噪声系数,增益,S参数仿真,谐波仿真,systemvue是仿真LNA在系统中的作用,一般模型是给定了NF 增益这些,看你需求。

Q:好的,前辈,那我可能要用ADS更符合一些。请问我是找芯片的封装模型做设计还是自己导入s2p文件做设计呀?因为我今天找了几款没找到直接ads能用的封装模型,就不太清楚这个仿真应该怎么做。

A:如果能找到封装库优先用库,如果是国产,几乎没有。

Q:哦哦,好的前辈,非常感谢!

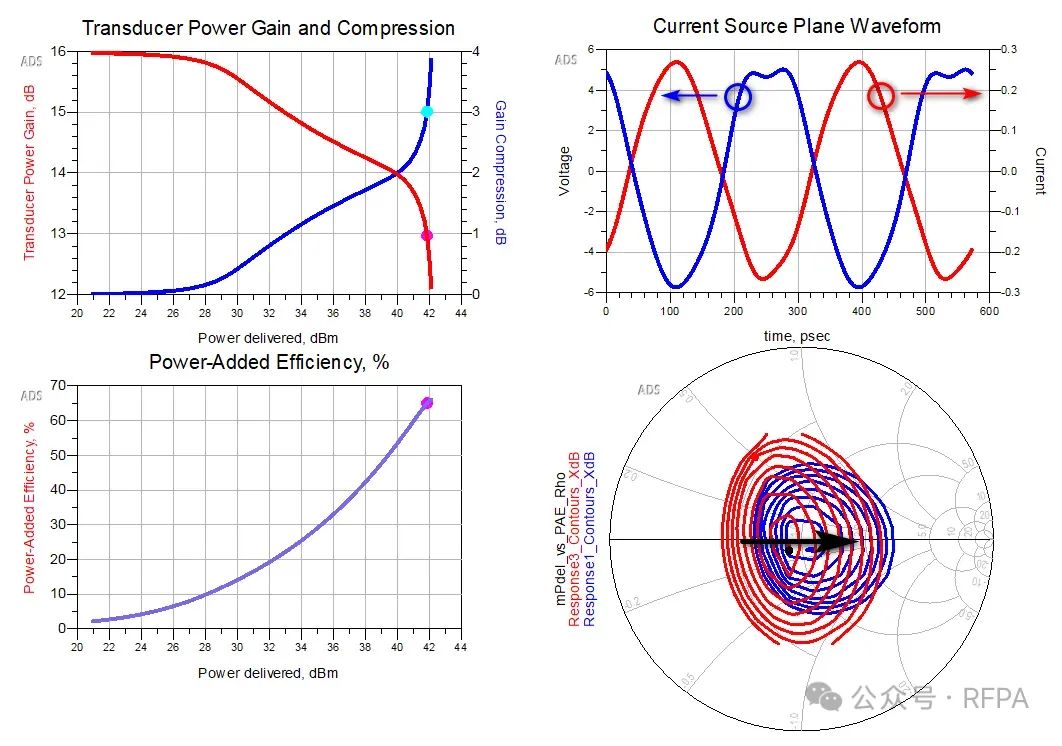

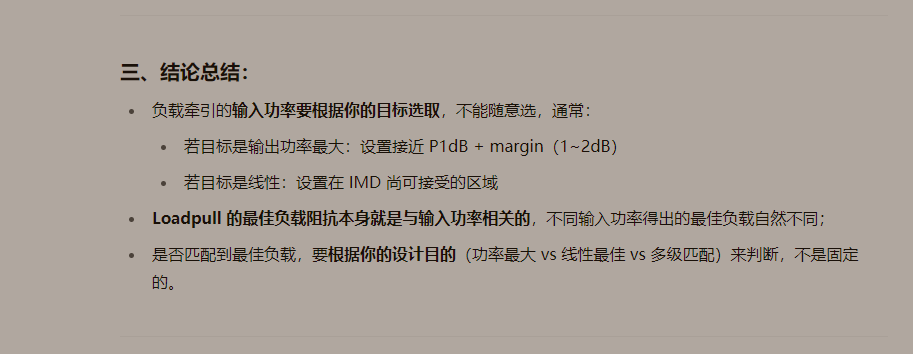

负载牵引时输入功率该如何设置?应参考哪个点的阻抗?

Q:想问一下负载牵引的时候输入功率应该设置为多少呢?我输入功率设置的不一样,最佳负载也不一样,另外一定要把负载匹配到最佳负载的位置吗?

A:loadpull可以扫描输入功率,评判最佳负载的标准是什么,你要先定下来,一般是3dB,压缩时对应的最大输出功率及效率。

Q:就是考虑最大输出功率的话,应该以哪一个输入功率的点去做loadpull呢?

A:要做扫描输入功率的loadpull,可以参考这个:《基于CGH40010F的寄生网络提取及PA Class分析 - Part I》

Q:我的输入功率改变,最大输出功率的圆心点一直在移动。

A:正常 。

Q:所以应该参考哪一个点的阻抗去做Loadpull呢?

我问AI说的是对的吗?

A:是对的,首先要确定你认为的最佳阻抗的标准 。

Q:

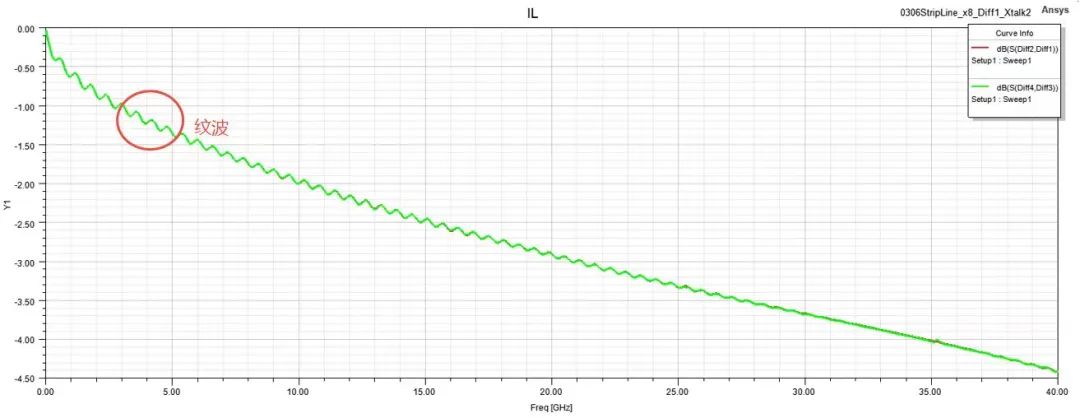

PCB 上长差分传输线的插入损耗为何有纹波?

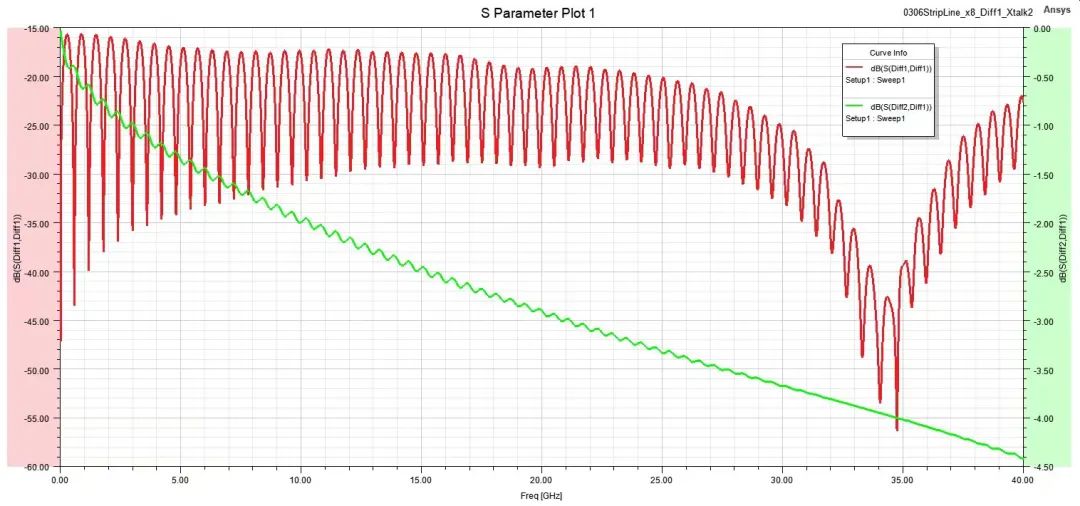

Q:请教一个问题,为什么PCB上长的差分传输线在仿真结果和实测的插入损耗都会出现一些小的纹波,这种纹波应该如何避免呢?(仿真中未考虑玻纤效应)

A:传输线多长?是匹配导致的吗?

Q:传输线大概140mm,回损在-15dB。

A:可能传输线阻抗不是理想的50欧姆,导致匹配周期性的变化。简单算一下,纹波一个周期大约0.6GHz,对应的二分之一波长为250mm,传输线电长度可以对应上这个数据吗?可以结合输入输出匹配情况看一下,纹波到波谷的频点匹配是不是比较差?

Q:好像确实是这个原因,电长度上也能对的上,这里的传输线两端分别连接SMA(50 Ohm)和42.5 Ohm的被测件,有一个阻抗突变点,有没有办法令传输线部分的回损变得更好一些呢?

A:传输线阻抗有一点偏,但是即使传输线特征阻抗是标准50,根据DUT阻抗计算回损大约-22dB。提升空间不大。

Q:好的,非常感谢!

5G 基站驻波检测的正常范围是多少?

Q:请教一下各位高手,5G基站的正常运行期间的驻波检测值通常是多少?多少就需要告警了?

A:2.5以下正常。

Q:谢谢指导,我再请教一下,基站实际功率40dBm,但是测试驻波用的测试信号只有20dB,对测试精度有影响吗? 尤其是馈线比较长,衰减比较明显的情况下。

A:基站设备本身是没有反射端口的,你所指的这20dB是指什么?是天端端口的耦合度?

Q:利用基站的DPD端口来检测返回来的信号。

A:那你说的是基站的功放输出到数字板上的了,20dBm太大了。

Q:请耦合器耦合的,有一定比例衰减的。

A:那要看你这衰减是多大了,0dBm都没问题。

Q:是的,感谢大神的讲解

A:

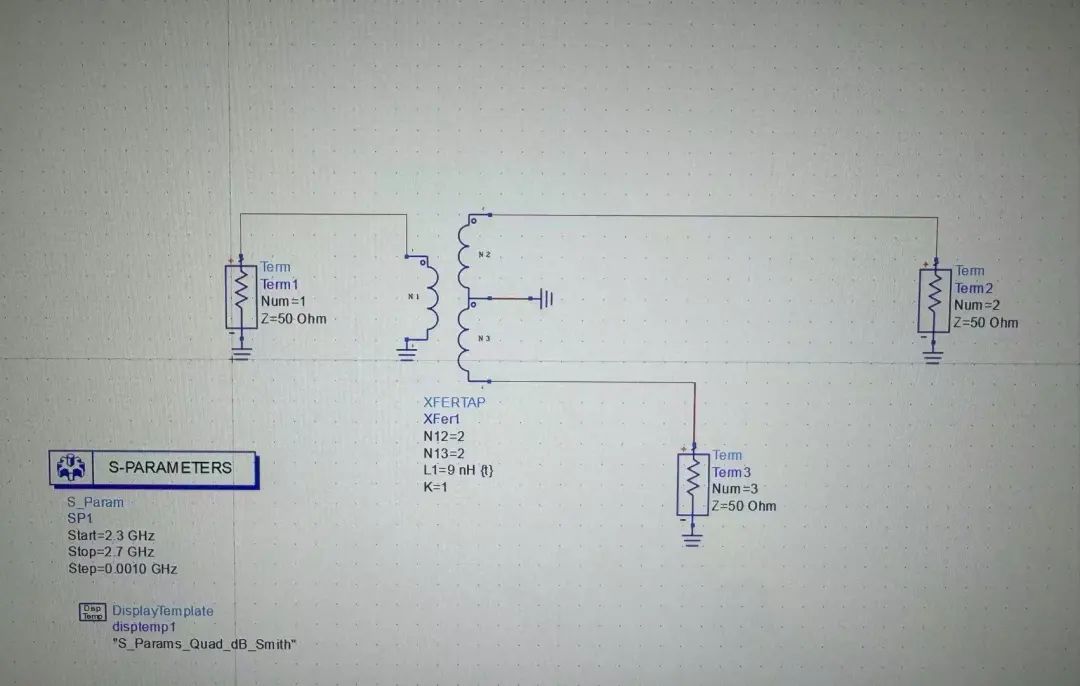

S22阻抗为10欧姆的原因是什么?与匝数比变换不符?

Q:这个S22阻抗为啥是10欧姆?匝数比变换过去不应该是12.5欧姆嘛?有老哥知道吗?

A:还有下面那匝N3的分流。

Q:可以方便写一下分析过程吗 ,困扰好久了,这个搞不明白没法做阻抗匹配

,困扰好久了,这个搞不明白没法做阻抗匹配

A: N12是前比后吗?

Q:是滴,大佬求救!

A:有个简单算法是n1n3可以看做是并联的(在你对2的端口那里算输入的时候)。n3和n1可以用阻抗变换比变到200欧和50欧并联,是40欧,再用和n2的阻抗变换变过去就是10。不太能叫并联就是可以合并算一下。

Q:那s11分析的话,就是50和50并联,然后等效回1端口就是100,谢谢老哥!

A:s11我感觉是400吧,你仿仿看。

Q:是100,我试了一下。

A:我以为对右边可以直接做个差分等效成100,看来不太行。

Q:s11我好像分析的不对,但是结果就是100。

A:没毛病,直接当并联看吧,我是当差分了想直接等效成跨接100再按2/1等效,但这样好像不太对。

仅用两端口网分能测试差分线的回波损耗和插入损耗吗?

Q:请教一下,手里只有两端口网分,可以实现对差分线的回波损耗和插入损耗的测试吗?

A:加两个巴伦可以大概测一下。

Q:那还得考虑balun的带宽,把巴伦去嵌掉。

A:是的,只能大概看看,两端口矢网测差分电路都是带巴伦测的。

Q: ,貌似只能转单端了。

,貌似只能转单端了。

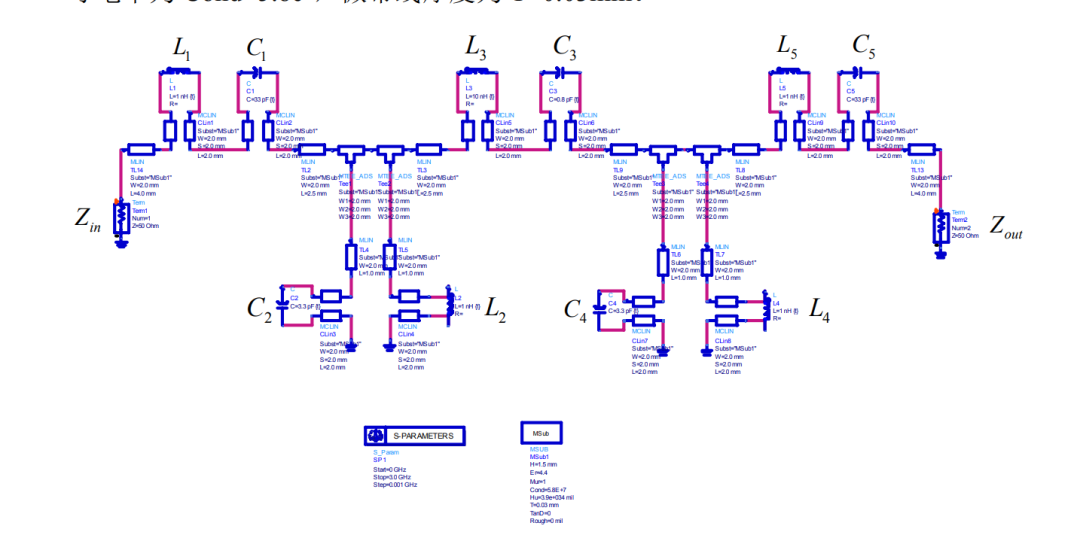

1GHz 带通滤波器尺寸小的原因是什么?

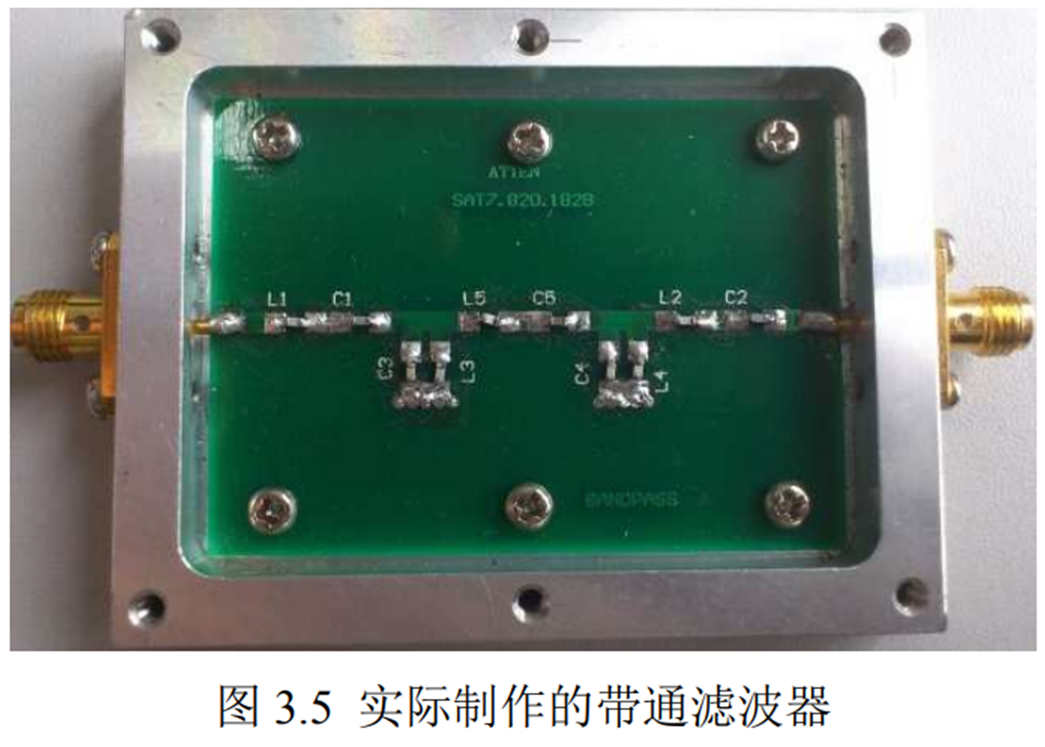

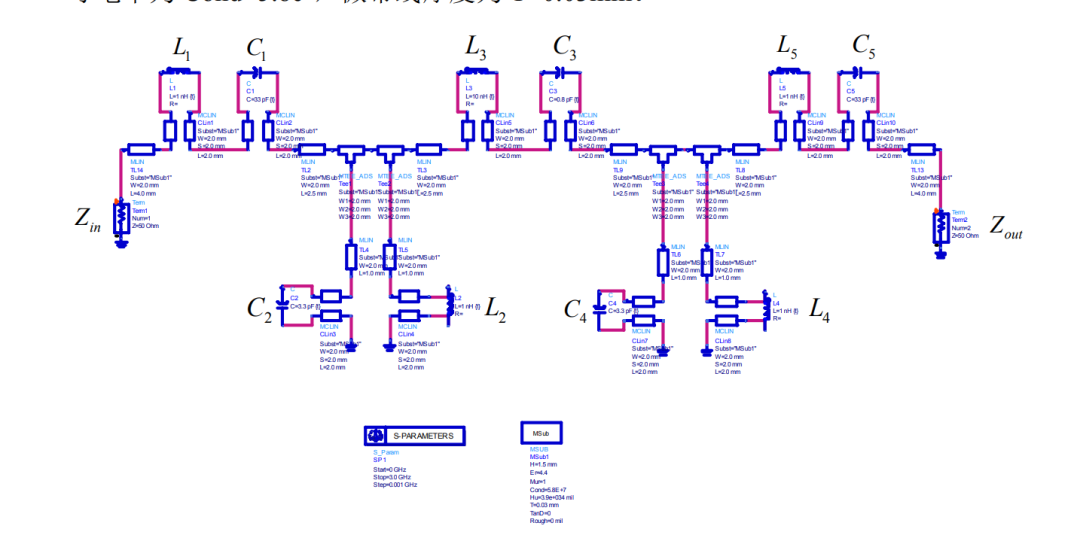

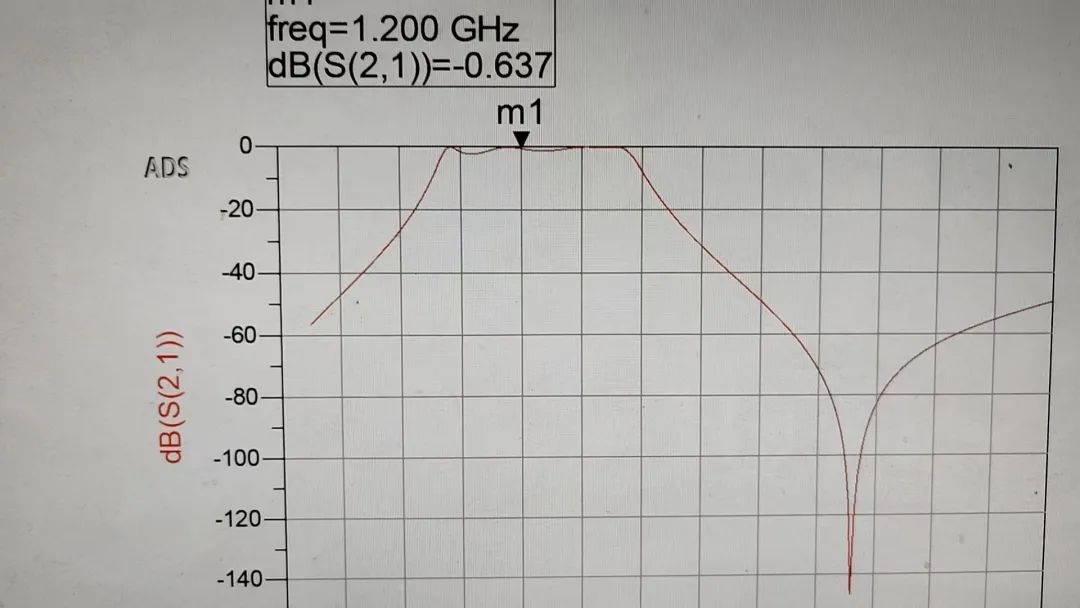

Q:友友们,别人论文里看到的,为什么他这个1GHZ的带通能做的这么小,他这种结构好像没怎么看过。

A:这个就切比雪夫LC带通啊, 很传统了。

Q:我用微带线匹配做出来的尺寸比他这个大多了,他这里面的传输线不会就是焊盘吧。

A:你看他最后的实物图呗。

Q:如下图:

A:那就是焊盘了。

A:这个是椭圆滤波器吧?LC并联,LC串联的,椭圆滤波器典型特征,相同阶数可以做到更高的带外抑制。

不好意思,应该不是椭圆,椭圆应该是串联,并联位置都应该是LC并联在一起。

慧智微精品问答群

————— 问 答 汇 总 —————

精品问答群的成员均来自往期精彩问答的活跃参与者,诚邀大家积极参与问答及文末的投票,加入精品群一起深度交流~

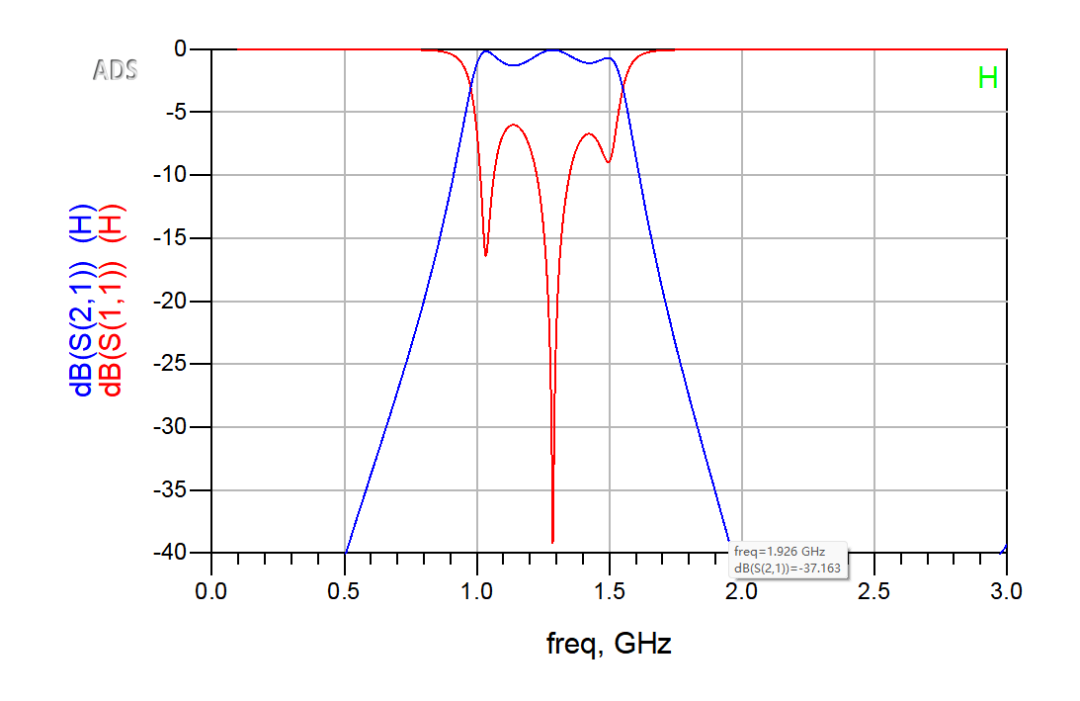

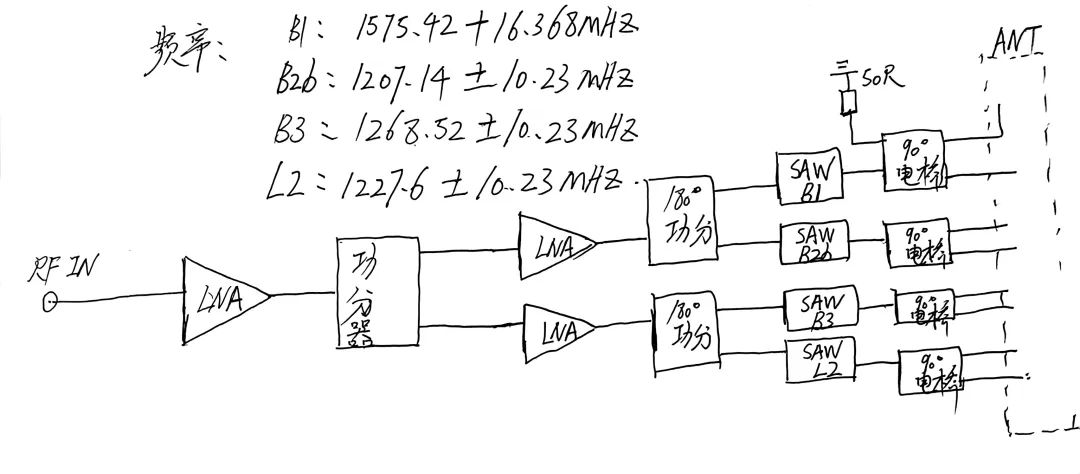

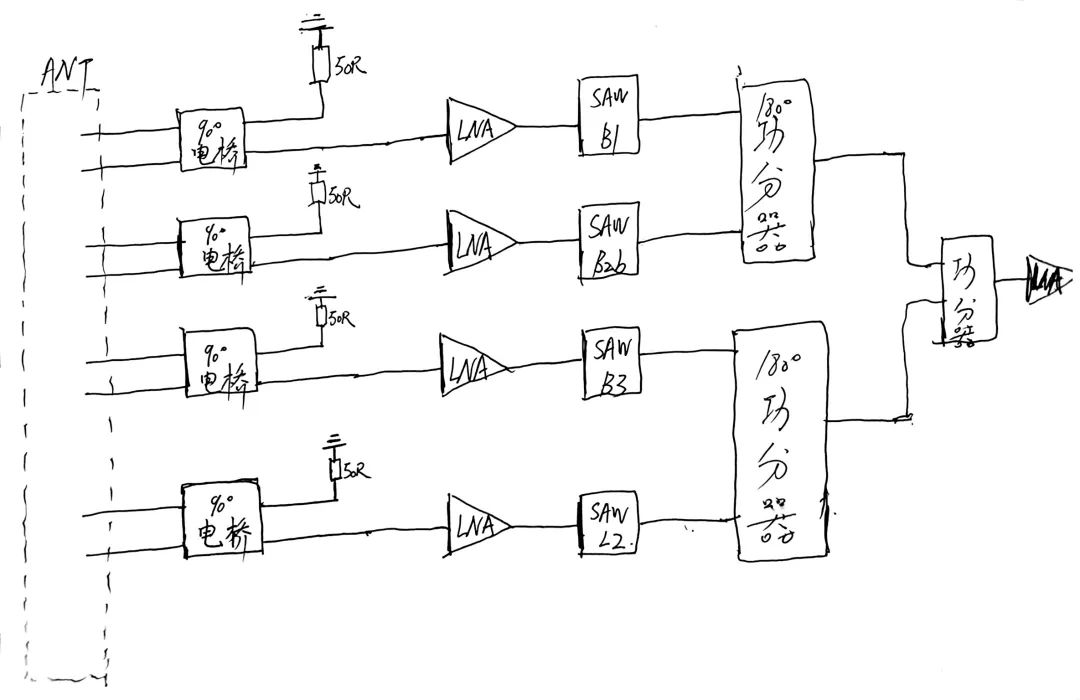

四频段高精度圆极化测量天线的馈电网络这样设计可行吗?

Q:家人们,一个四频段高精度圆极化测量天线我这样设计馈电网络有问题吗?

A:一般天线直接支持宽频接收,不需要四个天线,如果天线是有源高增益天线可能还好,如果用无源天线,过了电桥建议加LNA 然后四路一般直接一分四,各路也一样,没必要这样搞吧?

Q:我好像方向搞反了,我本来意思是说接收天线馈电网络,你意思是说这样不?

A:为啥需要四个天线,一般一根天线就支持GNSS多频段接收。

Q:可是电桥放前面有插损,噪声系数会抬高,是一个天线多馈点。

A:这个我上周想过,如果电桥额外插损比较小,电桥的噪声温度可以忽略,理想电桥 3dB电桥就没有。

Q:是的,一般电桥插损应该有3dB。

A:这个不需要考虑的,这不是额外损耗,这是分配损耗,不影响噪声。

A:电桥在这里作用是?

有大佬会TRX链路预算吗?

Q:有大佬会TRX链路预算吗?

A:要算哪些指标。

Q:比如说功率。

A:下载一个ADIsimRF。

Q:好滴,谢谢大佬!

同一LNA在不同工艺平台上增益提升但P1dB和OIP3下降,原因是什么?

Q:想请问一下佬们,LNA设计同一个在两个不同平台工艺上跑出来,对比baseline,GAIN提升,P1dB和OIP3反而下降有可能是什么原因呢?

A:工艺不同,管子的输出阻抗也不同,输出匹配要重新搭。

Q:但是看单级的S11和S22,反而是P1dB低的S11和S22更低,取dB,更负,这应该说明匹配会更好吧?

A:不会啊,你只关注最大功率效率传输,当然是gain越高,反射越低越好;但追求线性度和输出功率,要结合负载线匹配,看你侧重线性度还是侧重小信号增益。

Q:也是,就是说GAIN越高,反射越低只能保证进去的信号功率最大,不能保证转化成的基波最大(也就是非线性程度可能是不一样的)。这个还是要从输出阻抗那个角度去分析对吧?

A:嗯嗯,定性理解可以这样理解,具体还是参照准确定义。

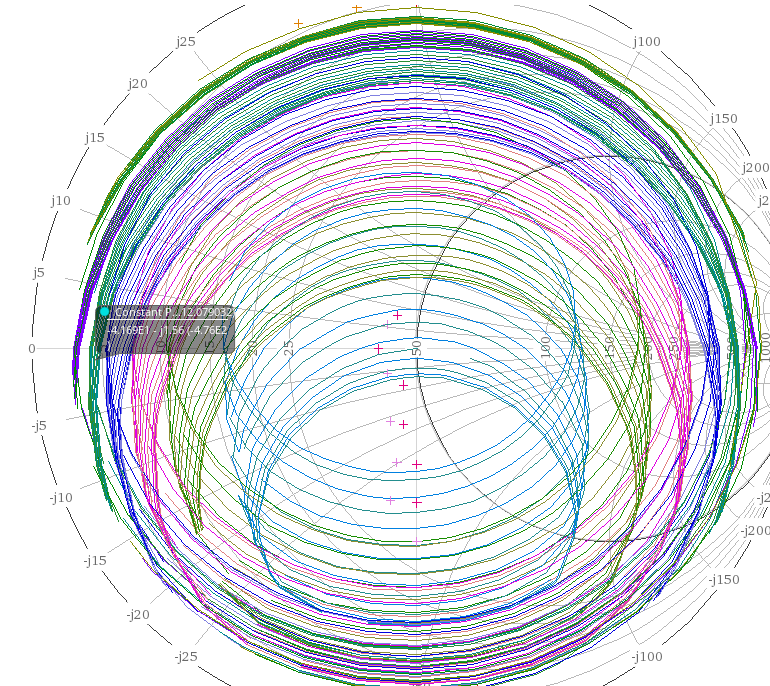

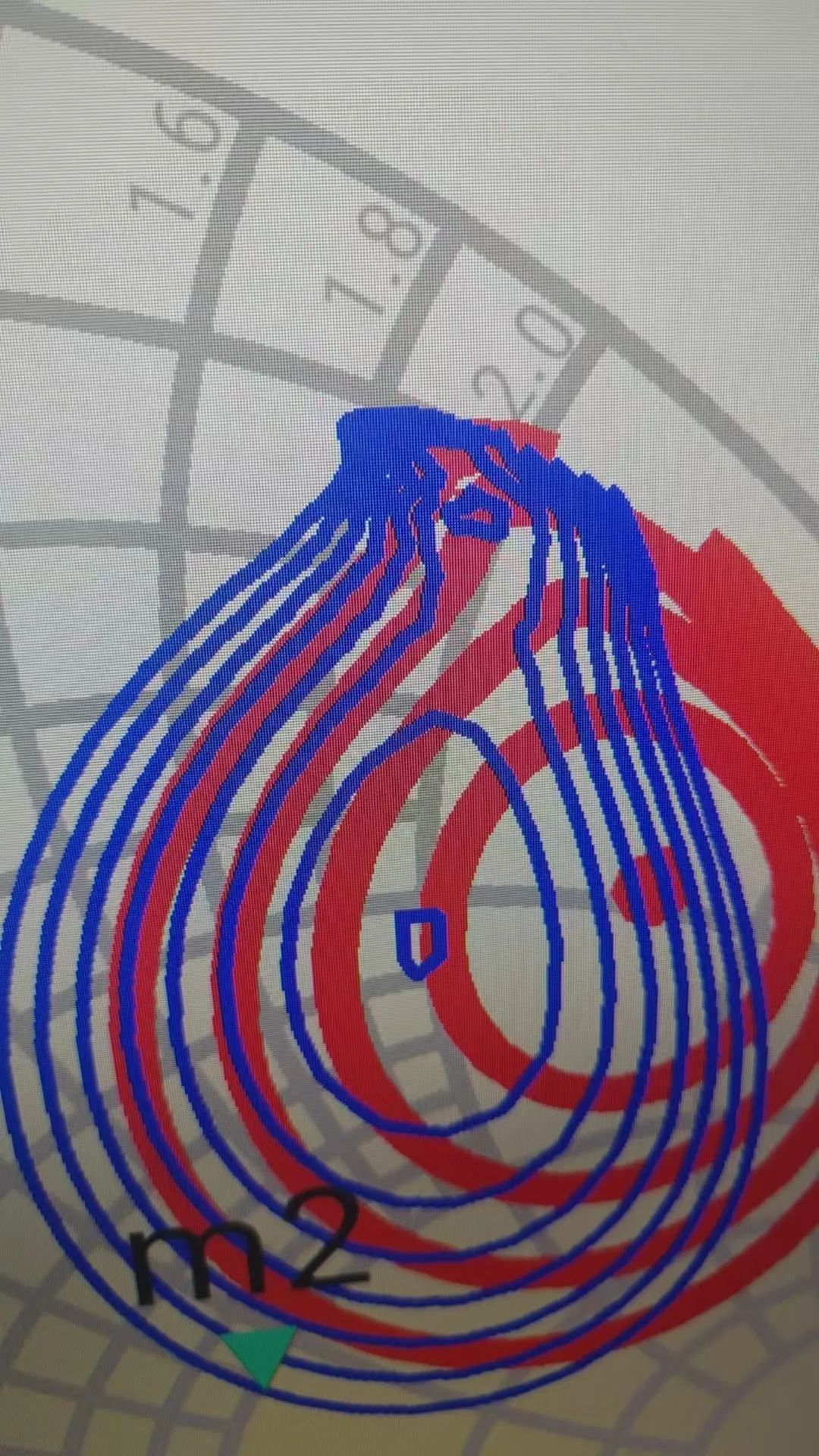

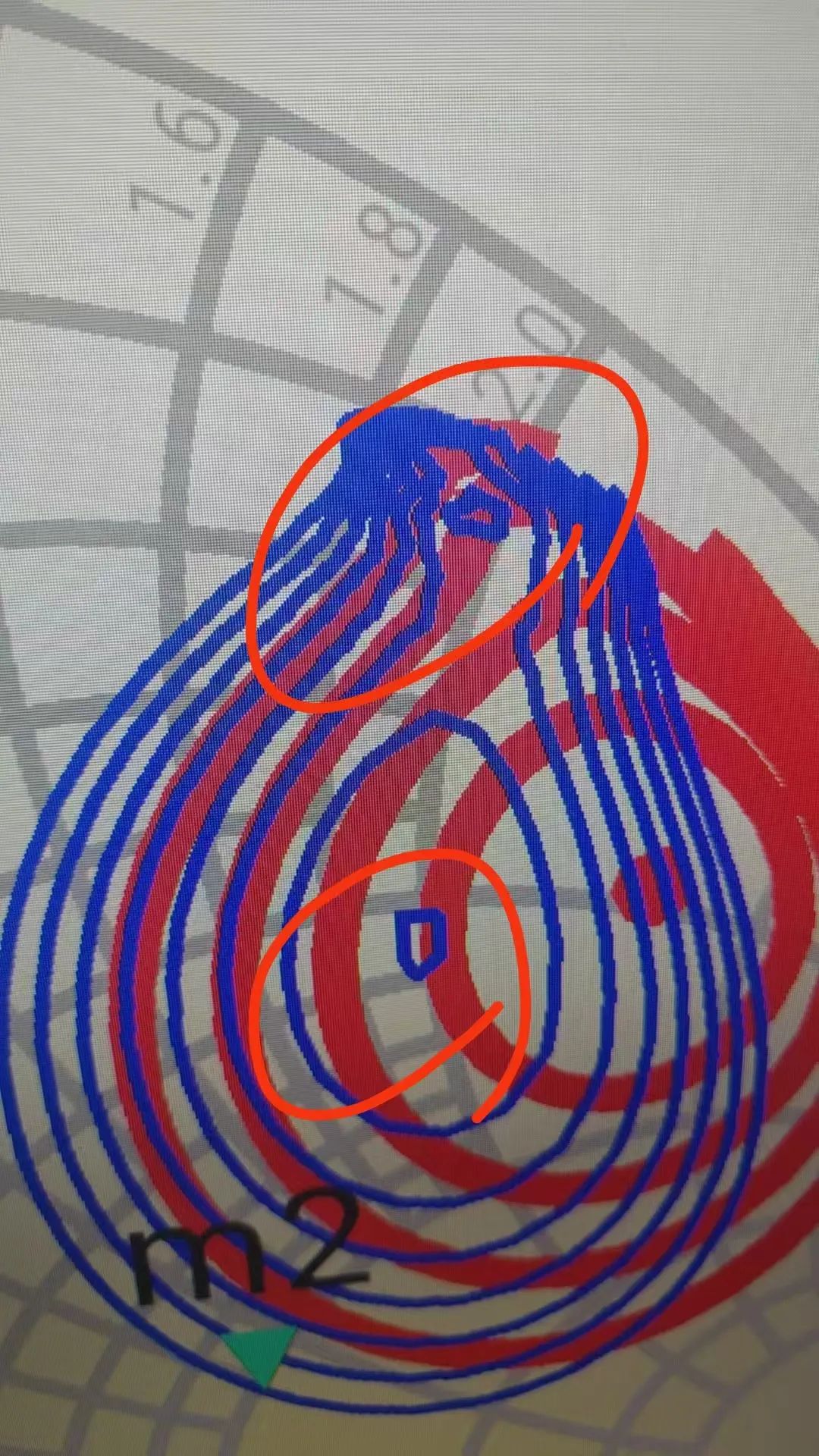

Loadpull出来两个圆心是啥原因啊

Q:请教下,Loadpull出来两个圆心是啥原因啊,谢谢。

A:PAE圆和pdel圆吧,跟刚刚的问题有点类似,功率最大不一定效率最高。PAE是基波比Pdc,进去基波大Pdc上升的比例可能更大,PAE就会更低。

Q:不好意思我没说清楚,我意思是这个功率圆看着有两个圆心。

A:要一个是等功率圆,一个是等效率圆吧。

A:有两个阻抗点输出功率或者效率一样,Mark点上去看看。

Q:功率是差不多,不过按照Loadpull理论,功率一样的点不应该形成在一个圆上?

A:不收敛了,或者可以调整一下归一化阻抗,看着就会顺眼很多。

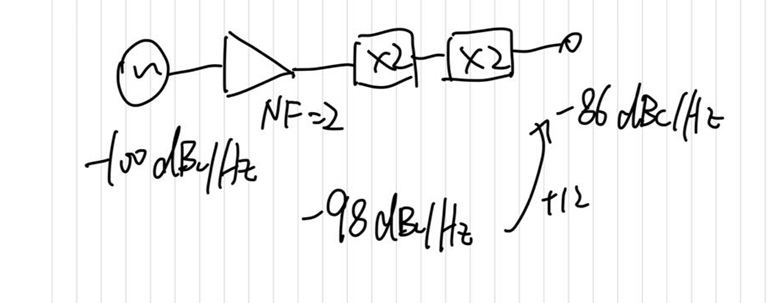

如何计算 LO 相位噪声的链路预算?总噪底如何确定?

Q:请问有没有大佬知道怎么计算LO phase noise的link budget?

A:系统一个整体的相位噪声,还是单独的LO。

Q:从PLL产生后开始算,经过4倍频和一些buffer,最后送到mixer。

A:可以噪声认为本振和中频不相关,线性相加,如果相位噪声差异有6dB以上,小的可以不用考虑了。

Q:假如我中频是2G,LO输入是6G,四倍频后是24G。

A:IF和LO相噪分别是多少?知道这个就能知道24G的了。

Q:LO和IF现在还没定,我想先知道怎么算。

A:如果中频是DDS产生 LO是PLL产生,一般LO占据主要因素,设为A 四倍频就是A+12dB,可以看看源设计的相关毕业论文,知网很多的,关键词 低相噪。

Q:有推荐吗?

A:S频段小步进、低相噪频率合成器的研究。

以上就是本期全部问答内容了,这期中的问答中,哪个是您心目中最精彩的呢?欢迎投票

针对以上问答您有不同的见解吗?欢迎在下方留言区说一说哟,同时也非常欢迎大家补充科普相关知识,或是分享讨论过程中那些有意思的观点~

我们将给精彩留言送上慧智微笔记本一个

我们还做了以下内容,希望能帮到你~

版权声明

本文仅作者转发或者创作,不代表旺旺头条立场。

如有侵权请联系站长删除

- 1 真有热量为 0 的蜜雪冰城!实测23杯这几杯热量惊人,千万别点! 前两个月咱们测了鲜奶茶,评论区和后台都在问——为什么没有蜜雪冰城?!不是我们看不上,而是—— 4 块钱的柠檬水,值得一个专场~今天蜜雪冰城热门款评测,它来了我们根据店里的菜单真鲜果茶、醇香奶茶&芝士奶盖、新鲜冰淇淋几个板...

- 2 2024阿那亚访客问答|海边假日生活全指南,收藏本篇,即刻出发! 编者按: ...

- 3 亲爱的妳 | 女教师的「智性衣橱」 ...

- 4 NEW IN | 秋风起,印花依旧迷人 ...

- 5 本周活动指南,暑期观影夏令营,萌宠运动会...更多精彩尽在漳州台商万达! ...

- 6 ETF投资知识5 | 手把手教你ETF如何买卖 ETF怎么买?ETF虽然也是基金,但是他的交易方式却等同于股票。因此,想要买卖ETF,首先要有个可以买卖股票的股票账户,还未开通股票账户的投资者可参阅《民生证券开户指南》。然后,投资者们只需要在自己的“民生财富汇App”中输入对应的ETF代...

- 7 阿那亚美食攻略|60+餐厅主厨推荐菜!收藏此篇,一文尽览不能错过的招牌菜 编者按:夏日正酣,正是向海边出发的好季节。旅行中的美食,是风味与记忆的邂逅,也是最抚人心的烟火气。寻访美食的过程,充满期待和惊喜;遇见令人心动的菜肴,便对一座城、一片海有了惦念。海边小镇,既有远近闻名的热门餐厅,也隐藏着不少惊艳一方的小众美...

- 8 权威发布丨辽宁何氏医学院2025年招生简章(文末附2025年招生计划) 高考落下帷幕全新征程即将开启欢迎报考辽宁何氏医学院为梦想奔跑的你必将在美丽的童话镇成就不一样的自己辽宁何氏医学院位于国家教育部、发改委等九部委提出建设的光明小镇的中心,是经教育部批准设置、由留学归国医学博士、全国防盲技术指导组副组长、国际眼...

- 9 根网科技祝您中秋快乐——月满人圆 喜乐安康! 皓月当空,心海澄明君之所想,吾志所向...

- 10 党的二十届三中全会公报一图读懂 来源:新华社免责声明:以上内容基于本公司认为可靠的已公开信息整理形成,民生证券力求但不保证内容的准确性和完整性,不保证已做最新变更。以上内容仅供参考,不构成民生证券做出的投资建议、收益承诺或对任何观点的认可。投资者应自主进行投资决策,民生证...

- 🧧年终回顾 | 致我们共同的二〇二五 2小时前

- 策马扬鞭启新程 | 智顺科技恭祝新年快乐 16小时前

- 【经济热点】地方两会经济“拼”图丨2026年三大国际科技创新中心建设启新篇 17小时前

- 《暗恋者的救赎》温情收官讨论不断 女性互助照见现实回响 17小时前

- 春光映征程,实干绘岚图 18小时前

- 相约AWE2026,锁定E2馆2F21,加西贝拉邀您共探制冷新可能 21小时前

- 噩耗!沉痛悼念周炳琨院士 22小时前

- 金山云星流平台上线MiniMax M2.5模型 23小时前

- 咖啡到底健不健康?记住这6个喝法,好处多多还避坑 1天前

- 创通联达在embedded world 2026发布基于高通跃龙™IQ10的TurboX IRB10开发公板及参考设计 1天前

旺旺头条

旺旺头条

发表评论:

◎欢迎参与讨论,请在这里发表您的看法、交流您的观点。